- I2C

- Inter-Integrated Circuit. Also called IIC, I2C. A two-wire, serial, half-duplex, master-slave data bus protocol created by Philips Semiconductor in 1982 to link the processor with peripheral devices, such as RTCs and EEPROMs, in embedded systems. It relies on open-drain technology – the signal line is pulled high when idle or sending a binary 1, and pulled low for a 0. It’s cheap to implement, but not very fast. It offers built-in addressing, unlike the faster SPI. Its two signal lines are serial data (SDA) and serial clock (SCL). It’s particularly good for controlling a number of slave devices that require only intermittent access. It uses 7-bit addresses, from 0 to 127, but addresses 0-7 are reserved for bus-management functions.

- SMBus (System Management Bus) is a stricter subset of I2C. Compare CAN, LIN.

- I2P

- Invisible Internet Project. A free, open-source darknet software program. Also, the online community that uses it.

- IA-32

- Intel Architecture 32. Another name for x86-32.

- IA-64

- Intel Architecture 64. (2001) Joint Intel/HP 64-bit, EPIC-based CPU architecture, also called Itanium. The market preferred AMD’s less radical x86-64.

- IAB

- Internet Architecture Board.

- IANA

- Internet Assigned Number Authority. A non-profit organization dating back to the early ARPAnet that manages the worldwide allocation of IP address blocks to RIRs. It became a department of ICANN on 1 January 1999 after the death of Jon Postel, its founder and longtime manager.

- I and Q

- See I/Q.

- IBM

- International Business Machines, originally. A very big computing & technology company. In addition to producing its own 80386 and 80486 CPU chips (see Intel) in the 1980s and 1990s, it makes server/workstation processors that mostly run Unix, Linux, or some other *nix OS; see PowerPC.

- IC

- Integrated Circuit. A single semiconductor chip that contains a complete, multi-element circuit.

- ICAM

- Identity, Credential, and Access Management. Security policies and practices to ensure that only authorized individuals have access to protected data or systems.

- ICANN

- Internet Corporation for Assigned Names and Numbers. The non-profit overseer of the Internet, launched in October 1998 and based in Marina Del Rey, CA. It manages the Domain Name System (DNS), assigning numeric IP addresses and creating new Internet domains – functions previously handled by the IANA and NSI, respectively. It sub-contracts some of its registration work to private companies, notably VeriSign, which has the .com contract.

- ICANN has had would-be competitors assign IP addresses in unofficial top-level domain names, such as .inc and .mp3, for clients. Addresses on these domains won’t be resolved by DNS root servers. Those who wish to access them must go through an alternate root server that maintains records of such domains. See RIR.

- ICC

- Integrated Circuit Card. Any of a variety of so-called smart cards, rugged plastic cards with embedded circuitry and electrical contacts for plugging into standard slots. Some contain only non-volatile memory, almost always flash memory. Others have logic circuits and volatile memory to support them. See MMC, PC Card, SD Card, SIM, and UICC.

- ICD

- In-Circuit Debugging. A technology for debugging software that’s running on an embedded microprocessor or microcontroller. It relies on circuitry, such as a JTAG interface, built into the embedded device to allow an external debugging program to start, stop, and monitor the running code.

- Most in-circuit debuggers leave the target processor in its host circuit board, and have a debug bus connecting to that circuit from external adapter hardware. Some instead use a development board into which the target processor must be mounted. (Strictly speaking, that’s no longer in-circuit, and means debugging can’t use any of the actual host board’s circuitry.) Either way, it’s all controlled by debugger software on a development PC that’s connected to the adapter or development board via some general-purpose interface: serial cable, Ethernet, USB, etc.

- ICD serves the same purpose as the older in-circuit emulator (ICE), with which it’s often confused. Because it runs the software on the actual target, it’s simpler, but also less powerful. When the added circuitry is part of the embedded microprocessor or microcontroller rather than just being on the host circuit board, the technology is often called on-chip debugging (OCD).

- ICE

- (1)

- In-Circuit Emulator. Hardware with its own microprocessor that it uses to emulate an embedded microprocessor or microcontroller in a target system for debugging purposes. It runs software that was created for the embedded device, and allows developers to start, stop, monitor, and make changes to the running program using debugger software that’s on a development PC connected to the emulator.

- Older ICEs physically replaced the target processor: developers would remove it from the target system, and then connect an adapter cable from the ICE to the empty socket. Newer ones use various methods to connect to the target without removing its embedded processor, but they still use their own processors to run the software.

- The ICE is often confused with the simpler but less capable in-circuit debugging (ICD), which achieves the same goal in a different way. It’s also not the same as in-circuit simulation, which simulates the target processor entirely in software.

- (2)

- Internal Combustion Engine. See engine.

- ICMP

- Internet Control Message Protocol. Part of the TCP/IP protocol suite at the Internet layer (the Network layer of the OSI model), used by gateways and servers to communicate routing error & diagnostic information, such as TTL timeouts and PING request/response. ICMPv6 also does multicasting and maps MAC addresses to IP addresses, tasks that version 4 left to other protocols – IGMP and ARP, respectively.

- ICO

- (1)

- Intermediate Circular Orbit. Another term for medium earth orbit (MEO). Also, the name of a global-coverage satellite telephone consortium that spun off from Inmarsat, went bankrupt, and was bought by Craig McCaw et al. Their main project, nowhere near complete as of 2007, is to be a bent-pipe architecture (i.e. satellites relaying signals between user & ground station) with 10 birds plus 2 spares in two 10,390-km altitude, 360.9-minute period circular MEO orbits inclined 45° to the equator. Mobile units will use 1980-2010 MHz uplink (lower S-band) and 2170-2200 MHz downlink. The 12 ground stations will use C-band uplink and downlink, roughly 5 and 7 GHz, and will be linked by a global high-speed IP network called ICONET. Compare Globalstar, Inmarsat, Iridium, Orbcomm.

- (2)

- Initial Coin Offering. The debut of a crypto-currency. Bitcoin was the first of the crypto-currencies, but there are many others.

- ICS

- Industrial Control System. See SCADA.

- ICT

- (1)

- Information and Communications Technology.

- (2)

- In-Circuit Testing. Testing individual components of an electronic circuit for faults. Contrast FCT.

- IDAPI

- Integrated Database Application Programming Interface. See API.

- IDC

- Insulation Displacement Connection (Contact). A quick method of terminating an insulated wire to a connector. The wire is forced into a V-shaped fork or tube terminal with small blades on its inner edges. The blades slice through the insulation to make contact. This is a common termination method for ribbon cables using headers with 0.156" (4mm), 0.100", 0.079" (2mm), or 0.050" pin spacing. Typically, the headers use two rows of contacts, so the mating ribbon cables have a pitch (wire spacing) that’s half that of the header.

- IDE

- (1)

- Integrated Drive Electronics. Western Digital’s 1986 drive-control technology, which put the electronics that run a disk drive (hard drive, floppy drive, CD-ROM drive) onto the drive itself, instead of on the motherboard. Two IDE-compliant drives, configured as master and slave, can share the same 40-pin, 2" wide ribbon cable.

- Disk drives using IDE and the ATA bus were standard in the PC industry for many years, and are referred to as IDE or IDE/ATA drives. The industry moved to SATA drives in the 2000s.

- (2)

- Integrated Development Environment. A GUI for developing, testing, and debugging software programs. It commonly comes with a set of compilers, a debugger interface, and other programmer tools.

- ideal gas

- A model for the behavior of gases, defined by the equation PV = nRT: pressure × volume = moles × universal gas constant × temperature. The universal gas constant R = 8.314 joules/moles-Kelvin.

- IDF

- Intermediate Distribution Frame. See distribution frame.

- IDFA

- Identifier For Advertisers. A unique character string assigned to each Apple mobile-telephony device. Apps on the phone use it to track the activities and physical location of that device (and its owner), usually for advertising purposes. Starting in 2016, Apple changed iOS privacy settings to allow users to set the IDFA to an all-zero string, which renders it largely ineffective if users are aware of the capability and choose to use it. In 2021, Apple finally changed IDFA sharing for apps to opt-in rather than opt-out, and roughly 96% of users chose not to opt in. The equivalent on Android devices is the AAID.

- IDL

- Interface Definition (sometimes Description or Design) Language. A language for specifying software interfaces so that different programming languages can access them in a consistent way. The original, C-based IDL was general-purpose. Now there are many IDLs tailored to a variety of environments and applications, and able to map to many programming languages.

- IDPS

- Intrusion Detection and Prevention System. See IPS.

- IDS

- Intrusion Detection System. A combination of security mechanisms and procedures for detecting malware exploitation of a network or individual computer. There are two IDS approaches: signature detection (comparing network traffic to a database of known attack behaviors) and anomaly detection (comparing network traffic to a normal pattern). Because of this focus on behavior, IDS can spot malware after it’s gotten in, but usually can’t block the initial infection.

- IDT

- (1)

- Integrated Device Technology, Inc. US semiconductor company. Its Centaur Technology subsidiary was briefly in the low-end x86 CPU business before being sold off to VIA Technologies in 1999. Their sole product, the IDT-C6, was a stripped-down 586. It dispensed with superscalar pipelining, superpipelining, out-of-order and speculative execution, branch prediction, etc., and used large internal caches, high clock speed, and a smaller die size to compensate.

- (2)

- Inter-Digital Transducer. See SAW.

- IEC

- (1)

- International Electrotechnical Commission. An electronics standards body formed in 1906 and based in Geneva, Switzerland. They work closely with the ISO. ANSI holds the US membership.

- IEC Class 0 appliances, discontinued as a standard for safety reasons, have a single level of insulation and no earth ground. Class I devices have a metal chassis connected to earth ground (see grounding). Class II devices have no earth ground but require reinforced or two-level insulation. Class III devices operate from a low-voltage source and can do without grounding and insulation.

- (2)

- International Engineering Consortium. A non-profit education body formed in 1944 to support continuing engineering education and links between academia and industry.

- IEEE

- International Electrical and Electronics Engineers. A global professional body at www.ieee.org, formed on 1 January 1963 from the merger of the American Institute of Electrical Engineers and the Institute of Radio Engineers. They’re responsible for many technology standards. These standards have names such as IEEE-802.3, IEEE-802.11, IEEE-802.16, IEEE-1394, etc., but in common parlance (and this site) they’re usually referenced by just the number, or by some catchier name such as Ethernet, Wi-Fi, WiMAX, or FireWire.

- IETF

- Internet Engineering Task Force. A self-organizing international professional group headquartered with ISOC in Reston, VA. Its working groups set Internet standards. They meet four times a year to argue about that.

- IF

- Intermediate Frequency. Given a high-frequency signal that’s been modulated to carry information, mixing it non-linearly with another high frequency produces a signal at a much lower frequency but still carrying the original signal’s modulation. This is the IF. See heterodyning.

- IFF

- Identification Friend or Foe. A transponder identification system, usually for aircraft. Early (World War II) models were passive devices, tuned to strongly reflect frequencies used by friendly radar.

- IFFT

- Inverse Fast Fourier Transform. See Fourier transform.

- iframe

- Inline Frame. An HTML element that allows a Web page to display content from another site without redirecting the user to that site. It’s very commonly used to show ads, so the hosting site often has no control over or even knowledge of what the iframe displays.

- IFSAR

- Interferometric Synthetic Aperture Radar. Used for 3D imaging.

- IG

- Integrated Graphics. Shorter form of IGP.

- IGBT

- Insulated Gate Bipolar Transistor. See transistor.

- IGFET

- Insulated Gate Field Effect Transistor. Another name for a MOSFET. See transistor.

- IGMP

- Internet Group Management Protocol. Part of the TCP/IP protocol suite at the Internet layer (the Network layer of the OSI model), IGMP handles multicasting on IPv4 networks. IPv6 networks instead have this capability as part of ICMP version 6.

- ignitron

- A mercury-vapor vacuum tube functioning as a high-power rectifier, i.e. converting AC to DC. It’s common in welding equipment. Current arcs from the (usually graphite) anode to a mercury pool cathode. See thermionic valve.

- IGP

- Integrated Graphics Processor. Also called iGPU. A GPU incorporated into a PC’s motherboard chipset or CPU module, or built into the CPU itself (see GEM). Demanding 3D graphics require the more powerful GPUs available only on discrete expansion cards, but the best IGP as of 2011 is sufficient for 2D and many 3D applications. See APU.

- IGT

- Insulated Gate Transistor. Another name for the IGBT.

- IGZO

- Indium Gallium Zinc Oxide. See semiconductor.

- IIPEC

- See IPC (3).

- IIR

- Infinite Impulse Response. A recursive (IIR) filter uses its own output as new input and could, therefore, continue to generate output indefinitely. In the language of Z-transforms, its response can contain poles as well as zeros. This means that it can be unstable, and lacks a linear phase response. On the other hand, it tends to have less complexity and time delay than FIR.

- Analog design permits only IIR filters. Popular approaches include Butterworth (all poles, maximally flat pass band & stop band, slow roll-off), Chebyshev I (all poles, equiripple pass band & flat stop band), Chebyshev II (poles & zeros, equiripple stop band & flat pass band), Bessel (flat passband & stop band, less attenuation of stop band, near-linear phase response), and elliptical/Cauer (equiripple stop band & pass band, sharp roll-off).

- IIS

- (1)

- Internet Information Services (formerly Server). Microsoft’s Web server application, overtaken in the 2000s by open-source alternatives.

- (2)

- Integrated Information Systems.

- ILA

- In-Line Amplifier. A signal amplifier incorporated into a communications line to boost the signal without delaying it, e.g. the EDFA.

- IM

- Instant Messaging. The older, PC-based form of texting. Compare IRC.

- image

- A disk image is a computer file that captures all the information needed to recreate the contents of a disk – a hard disk drive, CD, DVD, etc. ISO is the most common disk image standard.

- Image files are just files that contain pictures. The major non-proprietary formats are bitmap, GIF, JPEG, PNG, and TIFF. Bitmaps use no compression, JPEGs use lossy compression, and the others are lossless – although GIFs are limited to 256 colors. There are many more obscure formats, such as DWF.

- IMAP

- Internet Message Access Protocol. A member of the TCP/IP protocol suite at the Application layer, this 1996 e-mail retrieval protocol is used alongside the older, simpler POP. Unlike POP, it defaults to leaving messages stored on the mail server until the user’s e-mail client commands their deletion. This is a crucial difference for users who access messages from more than one device. IMAP uses TCP/IP port 143, or port 993 for encrypted connections. For mail transmission, see SMTP.

- IMD

- Inter-Modulation Distortion.

- IME

- Intel Management Engine. See ME.

- IMEI

- International Mobile Equipment Identity. A 56-bit wireless device ID number created for GSM to replace the too-short ESN. Unlike ESN and the newer MEID, which also identify the subscriber, the IMEI identifies only the device, leaving subscriber ID to the separate IMSI. On most phones, entering

*#06#on the keypad displays the IMEI. It avoids values that would require the characters A-F when displayed in hexadecimal form. - IMSI

- International Mobile Subscriber Identity. A unique 64-bit number assigned to each mobile phone subscriber. For the IMSI catcher, see stingray.

- IMSP

- Internet Message Support Protocol. Left uncompleted in favor of ACAP.

- IMT 2000

- International Mobile Telecommunications 2000. See 3G.

- IMT-Advanced

- International Mobile Telecommunications - Advanced. See 4G.

- IMU

- Inertial Measurement Unit. An instrument that provides real-time measurement of motion. The first versions relied on three mechanical gyroscopes to measure non-gravity acceleration, angular rotation, and in some cases orientation in 3-dimensional space. Modern ones use some combination of accelerometers, gyroscopes, and magnetometers.

- in-band signaling

- Using regular data channels to carry the control signals that govern establishing, managing, and releasing connections in a network. Compare with out-of-band signaling.

- incognito mode

- Google’s name for private browsing. See browser.

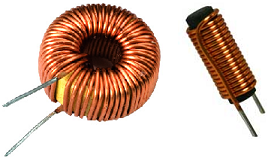

- inductor

- A circuit component consisting of a conducting wire coil around some sort of core. Current through the wire creates a magnetic field through the core. Inductance, denoted L for Russian physicist Heinrich Lenz (1804-1865), is the ratio of total magnetic flux to current through the device. The SI unit of inductance is the henry (H).

- For a given coil radius [r] and length [l] in cm, and a given number of turns N, an air-core inductor has inductance L = [ (0.394 r² N²) / (9r + 10l) ] µH, although this formula gets shaky if coil length is less than two-thirds of the radius. An iron core yields higher inductance, but also causes hysteresis and eddy current losses when the wire carries alternating current. Ferrite, which is magnetic but non-conducting, has only hysteresis loss. Cores are most often toroidal (donut-shaped) or cylindrical, depending on application. A toroidal inductor confines the induced magnetic field entirely within the core, reducing power loss.

- An ideal inductor L has an impedance Z defined entirely by inductive reactance X: Z = XL = jωL. However, small capacitances exist between the windings of any inductor, creating distributed capacitance Cd. This causes the impedance to increase faster with frequency than the model – until the resonant frequency, after which the impedance actually drops, eventually falling well below the model.

- Inductance can appear in devices that are not meant to be inductors. Any current will create a magnetic field. If the current is alternating, the magnetic field is constantly expanding and contracting, producing a voltage on the conductor that opposes the change in current. This is called self-inductance. All conductors exhibit it to some degree, although the effect is negligible in low-frequency circuits.

- InFLEXion

- A Motorola narrowband PCS technology based on FLEX that allows for voice paging and two-way voice messaging, with storage. See FLEX.

- InGaAs

- Indium Gallium Arsenide. See semiconductor.

- .ini

- Initialization. See filename extension.

- Inmarsat

- International Maritime Satellite, originally. The name is now International Mobile Satellite Organization, but the old abbreviation has been retained. This consortium was established in 1979 by members from ~60 nations, and became a private corporation in April 1999. Its purpose was to provide global (70° N to 70° S) coverage for maritime communications using 10 or 11 geosynchronous satellites. It has expanded into into other services, including aeronautical and land mobile comms. Compare Globalstar, ICO, Iridium, Orbcomm.

- InSb

- Indium Tin. See semiconductor.

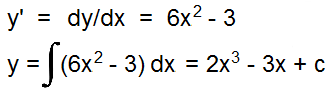

- integral

- One of the fundaments of calculus: the inverse of a derivative. That is, given some derivative dy/dx or y', called the integrand, its integral with respect to x is the function y – except that, since the derivative of a constant is zero, integration cannot recover any constant that was part of the original function. To account for this, the result commonly includes the character c to represent the unknown constant.

- Integrals can be either definite or indefinite. An indefinite integral obtains a function of an undetermined variable x, while a definite integral also evaluates the result of that function over some known range of values of the variable x to give a numeric result.

- Intel

- The leading manufacturer of PC microprocessors from the 1970s well into the 21st century. They created the now-famous tick-tock approach to developing new processors: first release an improvement of an existing architecture, typically by moving it to a smaller feature size (tick); then release a new architecture at the same feature size as the current one (tock). Repeat.

- In the early years, every reduction in feature size enabled a performance boost from faster system clocking, because the components of the CPU were physically closer to one another and signals between them took less time. Eventually, the heat buildup from ever-faster components packed ever closer together made it impractical to keep speeding up the clock. Intel, and its rival AMD, turned instead to multi-core architectures to keep improving CPU performance, and software has had to adapt with support for multi-threading and multi-processing.

- By 2016, with reductions in feature size becoming much harder to achieve (case in point: EUV lithography), Intel moved from the tick-tock approach to a new development cycle called Process-Architecture-Optimization (PAO).

- Some of Intel’s processors (and, for 80386 and 80486, similarly-named knockoffs by other companies), in chronological order:

- 4004 – (1971) Widely considered the world’s first microprocessor, i.e., with all its circuits on a single silicon chip. It had a 4-bit data bus, 740 kHz system clock, and 10 µm feature size, and could address up to 4 kB of RAM. Manufactured in 16-pin DIP form factor, it was used mainly in calculators.

- 8008 – (1972) 8-bit, 500 to 800 kHz CPU on 10 µm process. Made as an 18-pin DIP, and used for early hobbyist home computers.

- 8080 – (1974) 8-bit CPU with 2 to 3 MHz clock, and a 16-bit address bus supporting up to 64 kB of external RAM. 6 µm process, 40-pin DIP form factor. It was used in the Altair home computer kit; see PC.

- 8085 – (1976) 8-bit CPU with up to 8 MHz clock, and 16-bit address bus for up to 64 kB of RAM. 3 µm process, 40-pin DIP or 44-pin PLCC. Used just +5V DC power, rather than multiple voltage levels like the 8080.

- 8086 – (1978) 16-bit CPU, 4.77 to (eventually) 8 MHz clock, 20-bit memory addressing for up to 1 MB of RAM, 3 µm process, 40-pin DIP form factor, TDP 1.84W. This ground-breaking chip also debuted the highly successful x86-16 instruction set. PC clone-makers used the 8086, but IBM didn’t until the PS/2 series.

- 8087 – Math coprocessor to work with the 8086 or 8088 CPU.

- 8088 – (1979) Essentially an 8086, but with 8-bit rather than 16-bit external bus – the first hybrid CPU. This made computers based on it simpler and cheaper (and slower). IBM used the 8088 for its original PC.

- 8051 – (1980) 8-bit microprocessor. Many, many chips based on the 8051 architecture are still in use in 2009 as microcontrollers.

- 80186 – (1982) 16-bit CPU with 6 MHz clock (in initial versions), and 1 MB of internal RAM, hence 20-bit addressing. Because its actual bus is only 16 bits wide, its RAM uses logical addresses, each consisting of a 16-bit base address and a 16-bit offset. To convert a logical address to a 20-bit physical address, the processor bus interface unit (BIU) left-shifts the base address 4 bits, equivalent to a multiply-by-16, and adds the offset. Intel manufactured the 80186 until 2007 in several form factors. Other vendors have manufactured it since. It’s used for embedded devices, but saw little use in personal computers because its integrated timers, interrupt controller, and DMA controller weren’t compatible with motherboard hardware of the original IBM PC.

- 80286 – (1982) 16-bit CPU with 6 to 20 MHz clock, 24-bit memory addressing to support up to 16 MB of RAM, and 1.5 µm process, made in several form factors. Intel decoupled the interface to the expansion bus from the chip’s system bus, allowing the chip and motherboard to run faster without requiring a speed-up of the expansion bus (which would have affected the video and I/O peripherals). This was the first processor to be backward-compatible: it re-used the x86 instruction set of the 8086/8088, so it could run existing PC software. IBM chose it for their 1984 PC-AT. The 80286 was extensively cloned by other manufacturers.

- 80287 – Math coprocessor to work with the 80286 CPU.

- 80386 – (1985) 32-bit CPU, 12.5 to 33 MHz clock, and 32-bit memory addressing to support up to 4 GB of RAM. This chip introduced the x86-32 instruction set. It was manufactured on 1.5 and later 1.0 µm process in several form factors, including 132-pin PGA and PQFP. Compaq marketed the first 80386 PC. AMD pushed their 1991 classic 80386 DX to 40 MHz. With the 386, Intel began the practice of releasing different versions of each chip:

- 80386 DX – Retroactive name for the original 80386 after the debut of the 80386 SX.

- 80386 EX – A microcontroller version of the 386.

- 80386 SX – (1988) Scaled-down hybrid version with 24-bit memory addressing (supporting only 16 MB of RAM), and a 16-bit (instead of 32-bit) external bus.

- 80386 SL – (1991) Power-saving version of the 80386 SX, intended for portable computers.

- 80386 SLC – IBM’s power-saving version of the 386 SX, with an integrated cache that makes it a sort of 386/486 hybrid.

- 80387 – Math coprocessor to work with the 80386 CPU. Like the 80386, the 80387 was available with DX, SL, and SC designations.

- 80486 – (1989) 32-bit microprocessor with clock speeds from 20 (rarely) to 100 MHz and an integrated 8 kB L1 RAM cache. As with the 80386, Intel released different designations, listed below. AMD, Cyrix, and IBM also produced 486 chips using some of these designations. Some are 486 chips in name only.

- 80486 DX – Retroactive name for the original 80486 after the debut of the 80486 SX.

- 80486 DX2 – OverDrive 80486 DX with internal (but not external) clock speed doubled.

- 80486 DX4 – OverDrive 80486 DX with internal (but not external) clock speed tripled.

- 80486 SX – (1991) Really a 80486 DX with the internal math coprocessor disabled or, later, simply left out. It was to compete with cheap 386 clones from AMD and Cyrix. The 80486 SX was not a hybrid 16/32-bit chip, as the 80386 SX had been.

- 80486 SX2 – 80486 SX with internal (but not external) clock speed doubled.

- 80486 SL – Power-saving version of the 80486 DX, intended for portable computers.

- 80486 SLC – Cyrix/TI power-saving 16/32-bit hybrid version of the 486 SX, with 1 kB L1 cache.

- 80486 SLC2, SLC3 – IBM clock-doubled and -tripled versions of the SLC, with 16 kB L1 cache. SLC2 ran at 25 MHz externally, 50 MHz internally. SLC3 (Blue Lightning) ran at 25 or 33 MHz externally, 75 or 100 MHz internally.

- 80487 – Math coprocessor to work with the 80486 CPU. Like the 80486, the 80487 was available with DX, SL, and SX designations. The 80487 SX was a full 80486 DX, with some pins relocated so that consumers couldn’t instead use the cheaper 80486 DX as the math coprocessor; when installed, it electronically disabled the motherboard’s 80486 SX and took over as the CPU.

- Pentium – (1993) 5th generation, 32-bit, x86-compatible microprocessor. It would have been the 80586, but Intel learned the hard way with the 80486 that you can’t trademark a number. The original, 5th generation Pentium introduces the P5 core architecture, with a 5-stage pipeline and clock speeds debuting at 60 & 66 MHz. The 75-MHz Pentium has a 50 MHz front side bus. Intel has continued to re-use the Pentium name for CPUs built with later architectures.

- P54C – (1996) A Pentium with speeds up to 200 MHz and a divided L1 cache – 8 kB each for the instruction and data caches.

- P55C – (1997) Pin-compatible with the P54C, but using lower voltage. It has clock speeds up to 233 MHz, doubled (16 kB each) L1 instruction and data caches, and the MMX instruction set.

- Pentium Pro – (1995) 0.35µm process (except for the 150 MHz chips, which were 0.6µm), clock speeds 150 to 300 MHz plus, 60 or 66 MHz processor bus, 10- or 12-stage superpipelining, 16 kB L1 cache. The CPU and on-chip, core speed, 64-bit L2 SRAM cache (sizes 256 kB to 1 MB) are on a multi-chip module that requires a Socket 8 interface and a 6-layer motherboard. This is the first use of Intel’s P6 core architecture, really a RISC chip that translates CISC instructions into RISC machine language. It’s optimized for 32-bit applications, and doesn’t perform as well with 16-bit code. Intel designed it because they believed Microsoft would release its 32-bit OS (Windows NT) on schedule.

- Pentium II – (1997) Originally P6/Klamath. Intel created this 32-bit chip after getting burned on the 16-bit performance of the Pentium Pro. It’s an x86 Pentium Pro core with MMX support, 32 kB L1 cache, and clock speeds starting at 233 MHz. The standard 512 kB L2 cache is removed from the core to lower the cost. It’s on a Slot 1 SEC cartridge with the CPU, and has a 64-bit back side bus to the CPU at half core speed. The P6/Deschutes version of the Pentium II uses a 0.25µm process, and starts at 350 MHz.

- Celeron – Starting with the Pentium II and continuing through later versions of the Pentium and the Core i# processors, this is Intel’s name for the budget version of whatever its current desktop processor family is. It has the same packaging as the flagship design, but fewer features.

- The 1998 Celeron, based on the Pentium II, has 266/300 MHz clock, 250-nm Covington core, 32 kB L1 cache, no L2 cache, 66 MHz/32-bit FSB, and Slot 1 interface. Intel soon added an L2 cache and switched to Socket 370. Succeeding generations advanced clock speeds to 2.8 GHz, FSB to 533 MHz, and L1 cache to 128 or 256 kB. The Celeron D is based on a Pentium 4 90 nm Prescott core, with (2005) up to 3.06 GHz clock speed and Socket 478 or Socket 775 interface. The Celeron M is a notebook version (M = mobile).

- Xeon – Just as the Celeron series are low-end versions of whatever Intel’s leading processor at the time was, the Xeon family are heavy-duty server CPUs. The original Xeon (1998) was a 32-bit, 400 or 450 MHz Pentium II with a Deschutes core, 100 MHz FSB, and 512 kB to 2 MB off-die L2 cache on a 64-bit backside bus running at full core speed, all packaged in a SEC cartridge for Slot 2 interface. The Pentium III Xeon (1999-2000) has clock speeds of 500 MHz to 1 GHz, 100 or 133 MHz FSB, and 256 kB to 2 MB on-die L2 cache, and uses Slot 2. The 2005 generation is based on the 32-bit hyperthreading Pentium 4, with up to 3.66 GB clock, up to 677 MHz FSB, 512 kB to 1 MB L2 cache, and Socket 604 interface. (Older Pentium 4 Xeons use Socket 603.) In 2014, Intel announced a LGA-2011 socket Xeon chip with an integrated FPGA.

- Pentium III – (1999) The last of the 32-bit P6 line, debuted on 180 nm process at 366 MHz. The only real change from the Pentium II is the addition of the SSE instruction set. It has a 133 MHz front-side bus, uses Socket 370, and relies on Rambus RDRAM memory.

- Pentium 4 – 7th generation family that debuted in 2000 using the new 32-bit NetBurst architecture. The initial 180 nm Willamette core began with 1.3/1.4/1.5 GHz clock speed; eight 20-stage pipelines using speculative, out-of-order execution; L1 cache divided into 8 kB data cache and a new feature called Execution Trace Cache (estimated 96 kB); 256 or 512 kB L2 cache; double-clocked ALUs; a 100 MHz, 64-bit quad-pumped (making it effectively 400 MHz) system bus; SSE2; and Socket 423 interface. It initially required RDRAM, turning off many customers, but later versions work with SDRAM, DDR SDRAM, et al. After Willamette came the 130 nm Northwood and 90 nm Prescott cores. NetBurst was meant to deliver extremely high clock speeds, but, as of 2005, seems to be hitting its limit under Prescott: 3.8 GHz, with improved hyperthreading, 1 MB L2 cache, 800 or 1066 MHz FSB, Socket 478 or Socket 775 interface, and 13 new instructions for video encoding and floating point. Pentium 4 Extreme Edition appeared in 2003 using Xeon’s Gallatin core, plus 2 MB of L3 cache, but soon migrated to Prescott.

- Itanium – Also called P7/Merced and PA-RISC. A 7th-generation (2001-2002), 64-bit, 180 nm process, 733-800 MHz processor co-developed by HP and Intel for high-end servers. This is not an x86 processor – it has a new instruction set, IA-64 (see EPIC), that retains x86 backward compatibility, awkwardly, with 16- and 32-bit OSes. It wasn’t a commercial success.

- Itanium 2 – 2002 successor to Itanium, also developed with HP, and also not a hit in the market. 64-bit, 180 and later 130 nm process, 0.2-1.6 GHz clock. Montecito (2006) is a dual-core, 90 nm version with 12 MB cache per core, 1.4+ GHz clock, and multi-threading.

- Pentium D – A dual-core Pentium 4 with 90 or 65 nm process, 2.66-3.73 GHz clock.

- Pentium M – Notebook processor, 32-bit P6 core, originally (2003) 130 nm process, 64 kB L1 cache, 1 MB L2 cache, 100 MHz quad-pumped FSB (virtual 400 MHz), 0.6-1.7 GHz clock, Socket 479. Later 90 nm version has 2 MB L2 cache, 1.0-2.26 GHz clock, Socket 478.

- Core – (2006) Low-power, 32-bit, 65 nm, 1.66-2.166 GHz descendant of Pentium M. The Core Duo has two processors sharing a 2MB L2 cache, starting the market’s move away from ever-increasing clock speeds and toward multiple cores at less aggressive speeds. The Core Solo is a less common variant with only one functioning processor. Both use the 479-pin Socket M.

- Core 2 – (2006) 8th generation, 64-bit, 65 nm, 1.6-2.67 GHz processor with 2-4MB L2 cache. Official replacement for the Pentium brand. It comes in Core 2 Solo (one working processor), Core 2 Duo (two processors, sharing the L2 cache), Core 2 Extreme (2.93 GHz or 8MB L2), and Core 2 Quad (four processors). These chips use the 775-contact Socket T. In late 2007, Intel began producing 45-nm process Core 2 chips with an important innovation: a metal rather than silicon gate in the MOSFETs that are the building blocks of every processor, and a hafnium-oxide rather than silicon-oxide gate insulator. This lets transistors be smaller and faster with less gate leakage current.

- Atom – (2008) Small, very low-power x86 on 45 nm process, with TDP from 4W to less than 1W. 800 MHz to 2 GHz clock, 400 or 533 MHz FSB, 512 kB or 1 MB cache. Capable of running a very basic PC, but aimed primarily at the mobile and embedded device market, where it did poorly because it cost more and used more power than SoC-based rivals such as ARM.

- Core i# – (2008) This entry covers the first-generation Core i7, Core i5, and Core i3. Intel continues to use these names for CPUs built with later architectures, from Sandy Bridge on.

- Core i7 – (2008) 64-bit, 45 nm (Nehalem) or 32 nm process, for LGA 1156 (Socket H), LGA 1366 (Socket B), or µPGA-989 socket. It has 2.66-3.2 GHz clock (newer versions have Turbo Boost, which dynamically overclocks under load) and, normally, 4 cores, each with its own L1 cache (32 kB data, 32 kB instructions) and 256 kB L2 cache. The uncore, the section of the chip shared by all the cores, has an integrated memory controller (IMC), L3 cache, and multiple QuickPath Interconnect (QPI) links to replace the FSB.

- Core i5 – (2009) 64-bit, 45 or 32 nm process, 2.66 GHz clock. Uses LGA 1156 socket. Its 2 or 4 cores each have 64 kB of L1 cache and 256 kB of L2 cache, and share 4 or 8 MB of L3. It has Turbo Boost, which dynamically overclocks the CPU when needed. The 2010 dual-core models share a MCM with an integrated Intel HD Graphics GPU.

- Core i3 – (2010) Entry-level, dual-core CPU to replace Core 2. 45 or 32 nm process, 2.93 to 3.06 GHz clock, LGA 1156 or µPGA-989 socket, integrated Intel HD Graphics GPU.

- Sandy Bridge – (2011) Fully 64-bit, 32 nm revision of the Core architecture, combining controllers for memory, PCIe, and integrated graphics with 6 or 12 execution units on the CPU die. The System Agent (called the uncore in previous architectures) provides improved power management. The Sandy Bridge Core i3 is dual-core; desktop Core i5 and most Core i7 chips are quad-core. All models have integrated Intel HD graphics. Clock speed 2.5-3.5 GHz (Core i5 and i7 have Turbo Boost); L2 cache 256 kB per core; L3 cache 3, 6, or 8 MB for Core i3, i5, and i7 respectively; 65 or 95 W TDP; LGA-1155 socket.

- At the low end, there are budget Pentium G and Celeron G versions of Sandy Bridge that also use socket LGA-1155. At the high end, there are 6-core server versions of Core i7 with clock speeds up to 3.8 GHz, L3 cache of 10, 12, or 15 MB, 130 W TDP, and socket LGA 2011; and 6- or 8-core Sandy Bridge Xeon server chips with less aggressive clock speeds but up to 20 MB L3 cache and up to 150 W TDP, using LGA 1356, LGA 1366, LGA 1567, and LGA 2011 sockets.

- Ivy Bridge – (2012) A 22 nm improvement of Sandy Bridge (tick), with lower power consumption – TDP for the initial releases is 55, 65, or 77 W. Some budget Core i3 and i5 Ivy Bridge models lack L2 cache and/or integrated graphics.

- Haswell – (2013) 22 nm successor to Ivy Bridge, using socket LGA-1150. Tock. Debuting with 2 or 4 cores, clock rates from 2.0 to 3.5 GHz, 4 to 8 MB L3 cache, and TDP from 35 to 84 W. Low-power Core i3 versions for mobile devices have 1.3-1.8 GHz clock, 3 MB L3 cache, integrated graphics, and 11.5 W or 15 W TDP.

- Quark – (2013) Smaller successor to the Atom, using a 32 nm process. 32-bit, single core, 400 MHz clock, supports 800 MHz DDR3 SDRAM.

- Silvermont – (2013) A 22 nm die shrink of Atom/Quark.

- Braswell – (2015) 14 nm process, 2 or 4 cores, 1.04 or 1.6 GHz clock (turbo boost to 2.08-2.4 GHz), 1 or 2 MB L2 cache, Gen 8-LP graphics, TDP 4 to 6 W; models are labeled Celeron or Pentium, and are for mobile devices and very low-end PCs.

- Broadwell – (2015) A die shrink of Haswell (tick) to 14 nm. Its major selling points are a new, more powerful generation of integrated graphics (GT2 with 24 execution units, or GT3 with 48) and an estimated 30% reduction in power consumption. The Broadwell-K sub-family for desktop systems are exclusively quad-core i5 or i7 with 3.1 to 3.3 GHz base clock, 4 or 6 MHB L3 cache, 128 MB L4 cache, 65W TDP, and the LGA-1150 socket. The server versions use LGA-2011 (v3). The Broadwell-H, -U, and -Y are for low-power mobile devices, and use a BGA form factor to be soldered in place.

- Cherry Trail – (due 2015) 14 nm process Atom chip, 4 cores; slightly more powerful version of Braswell, meant for tablet PCs.

- Skylake – (2015/2016) 64-bit, 14 nm successor (tock) to Haswell/Broadwell, with DDR4 SDRAM support. The desktop versions use socket LGA 1151, have 256 kB L2 cache per core, and, as usual, come in dual-core (Pentium or Core i3) and quad-core (Core i5 or Core i7) models. Clock speeds range from 2.7 to 4.0 GHz, and TDP is 65 to 95 W. Core i3 and Pentium have 3 or 4 MB L3 cache, Core i5 has 6 MB, and Core i7 has 8 MB plus hyperthreading. Most models have Intel HD Graphics 530. The Xeon series for server processors also use LGA 1151. Notebook versions are expected to use a solder-down BGA form factor.

- Core i9 – (2017) Server-grade members of the Skylake family with 10 to 18 cores, 1MB/core L2 cache, 2.6 to 3.3 GHz base clock, and TDP 140 to 165 W. They use the LGA 2066 socket.

- Kaby Lake – (2017) Minor improvement on Skylake, still using 14 nm process and socket LGA 1151. No more tick-tock. Unlike previous architectures, Kaby Lake will not support any Windows OS other than Windows 10, and includes hyper-threading capability in even its low-end (Pentium) models.

- Cannon Lake – (2018) 10 nm die shrink of Skylake, for low-power mobile devices rather than for desktop or laptop systems.

- Coffee Lake – (2017) 9th generation update of Kaby Lake, still with 14 nm process and socket LGA 1151. Core i3 has 4 cores, Core i5 has 6, Core i7 has 6 or 8, Core i9 has 8. The Pentium and Celeron models are still dual-core.

- Comet Lake – (2019) 10th generation of Intel desktop processors, essentially a minor advance on Coffee Lake, still using 14 nm process and the same core counts, but the new LGA 1200 socket.

- Ice Lake – (2019) 10th generation mobile-platform processor family, using 10-nm process.

- Rocket Lake – (2021) 11th generation desktop processor family, still using 14-nm process and the LGA 1200 socket.

- Alder Lake – (2021) 12th generation desktop processor family, using LGA 1700 socket, with support for PCIe 4.0/5.0 and DDR4/DDR5 RAM. This generation introduced Intel’s hybrid design approach with two types of cores for the Core i5, Core i7, and Core i9: E-cores, optimized for efficiency with multi-threading, and P-cores, optimized for performance with one or a few threads. P-cores therefore have the higher base frequency. The desktop Core i5 has a mix of 6 or 10 cores, the Core i7 has 12, and the Core i9 has 16. The Core i3 isn’t a hybrid, having just 4 P-cores and no E-cores. The Celeron and Pentium versions of Alder Lake are dual-core. Each core has 1.25 MB L2 cache, and the cores share 4 to 30 MB of L3 cache.

- Raptor Lake – (2022) 13th generation desktop processor family, still using LGA 1700 socket with support for PCIe 4.0/5.0 and DDR4/DDR5 RAM. Also like its predecessor, Raptor Lake’s Core i5, i7, and i9 models are hybrid designs with a mix of P-cores and E-cores, while the Core i3 has only the P type. The desktop Core i5 has 10 or 14 cores, the Core i7 has 16, and the Core i9 has 24. No Celeron or Pentium versions of Raptor Lake have been released as of late 2023. Each core has 1.25 MB L2 cache, and the cores share 12 to 36 MB of L3 cache.

- Meteor Lake – (2023) 14th generation successor to Raptor Lake for mobile (laptop) applications, using the Intel 4 process, formerly called the 7 nm process. It’s a tile-based hybrid design, with some cores optimized for efficiency and others for performance. It uses the new BGA 2049 socket, and so is not available for DIY builds. The branding ditches the i used for previous generations and instead calls these CPUs “Ultra” – Core Ultra 5, Core Ultra 7. The processors include a neural processing unit (NPU) for performing AI tasks.

- Arrow Lake – (2024) Built with RibbonFET transistors, a gate-all-around (GAA) design, this is another tile-based design. It uses the new LGA 1851 socket, and adds support for PCIe 5.0.

- Intelsat

- From “International Telecommunications Satellite Organization”. An international body established in 1964 to develop global commercial satellite communications, reorganized in 2001 as a private company owned by its major telecom customers. The name also refers to the geosynchronous satellite system (more than 20 vehicles) it created and operates for telephone, video, & data services. See Comsat.

- interleaving

- Bursts of errors in a data-transmission channel can defeat FEC, which is mostly designed to handle random bit errors. Interleaving is the technique of separating the channel-coded symbols in time so that error bursts will be scattered over multiple codewords, enabling the FEC to overcome them. Of course, interleaving must be applied after channel coding at the transmitter, and removed before channel decoding at the receiver.

- Block interleaving stores coded symbols in an array by columns and outputs them by row, thus rearranging them in time. Convolutional interleaving uses a set of variable-length registers to add different delays to symbols. Convolutional interleaving creates less delay and uses less memory.

- Internet

- From “internetworking”. The worldwide network of networks. A good way to understand it is to think of it, not as a physical entity, but as a set of rules. A computer is part of the Internet if it follows these rules, which include using the TCP/IP protocol suite for connections, and being accessible to other Internet nodes by way of the public switched telephone network (PSTN) and a globally unique IP address.

- The Internet began as the DoD-funded ARPAnet in 1969 with four nodes, three of them in California. It expanded rapidly across the U.S., connecting universities and other research centers, and crossed the Atlantic by 1973. On 1 January 1983, ARPA dropped support for the ARPANET protocol, leaving TCP/IP as the sole and required language. This date is often pegged as the birth of the Internet. The DoD-only MILnet split off later that year.

- After the NSF rolled out its NSFnet backbone in 1986, it began assuming management responsibilities from the remaining ARPAnet, which formally ceased to exist in 1990. Other high-speed U.S. networks joined NSFnet to coalesce into the Internet backbone: the combination of core routers, network access portals, and high-capacity, long-haul telephone lines that carry and route Internet traffic. Starting in the late 1980s and continuing well into the 1990s, the U.S. government unsuccessfully pushed the networking community to replace TCP/IP with the OSI protocols.

- In 1989, the network began allowing commercial E-mail services access. The ISPs, having got their noses into the tent, pushed for more access and got it. The 1991 High Performance Computing Act sponsored by then-Senator Albert Gore, Jr., funded major expansions of the Internet’s infrastructure and capacity, and also the NCSA, creators of the first Web browser. The commercialization of the Internet followed quickly, utterly ruining it or bringing its benefits to the world, depending on your point of view. The tool for university researchers had become a medium of mass communication.

- Government-sponsored research centers and military or intelligence facilities responded by quietly moving to high-speed networks such as ESnet (Energy Sciences Network), Internet2, and the Defense Switched Network, which parallel and in some locations connect to the Internet but carry only their own traffic.

- The World Wide Web (WWW) is not the same thing as the Internet, any more than a bus service is the streets it runs on. It’s just a popular way of using the Internet. A server can be on the Internet, i.e., have an active connection and a dedicated IP address, without being known to the WWW or even to the DNS. In fact, that would make it part of a darknet, which sounds cooler than it is.

- No one runs the Internet, but there are many gatekeepers and rulemakers: ARIN, IAB, IANA, ICANN, IETF, ISOC, and W3C, just to start with. The NSF was the network overseer until 1998, when it relinquished that role to ICANN.

- intranet

- A private network using the same protocols and routing methods as the Internet.

- inverter

- A device that converts DC to AC. This includes the three-phase inverter for producing three-phase AC power. Solid-state designs have largely replaced the old mechanical switches. Inverters are more complicated and less efficient than rectifiers, which perform the reverse operation, AC to DC conversion.

- Photovoltaic (PV) installations that supply AC line power need inverters. It’s increasingly common for utilities to require that customers connecting their PV systems to the grid install smart inverters, which have two-way communication so that grid controllers can direct them to change their output and supply or absorb reactive power in response to changing grid conditions. The NREL has taken the lead in setting standards for such inverters.

- As PV installations proliferate, the current (2017) generation of smart inverters won’t be fast enough to deal with the resulting grid instability. The likely solution is virtual oscillator control (VOC), in which inverters detect dips or surges in grid power and respond by immediately and autonomously adjusting their output voltage. Large numbers of VOC-capable inverters all acting at once could, in theory, push or pull a grid’s AC frequency back to normal without the delays and costs of centralized command & control. They could also, pretty obviously, be hacked to crash a grid.

- I/O

- Input/Output.

- IOB

- Input/Output Block. The basic I/O unit of an FPGA.

- ION

- Intelligent Optical Network. A fiber network with optical switching and decision-making capability, as opposed to being a simple data pipe allocated and controlled from switching centers. This allows it to be more flexible and offer a greater range of services.

- ion drive

- A type of efficient but low-power spacecraft propulsion. It uses an electric or magnetic field to push out ions of a fuel material at very high speed, generating thrust in the opposite direction. This can’t even approach the power a boost vehicle needs, but is suited to steady, long-term acceleration and maneuvering in low-gravity environments.

- ionosphere

- A fluctuating shell of high ion density above Earth’s stratosphere. Its base is at about 60 kilometers, and it extends to an indefinite height, so it overlaps the highest three layers of the atmosphere. It’s conventionally divided into the D-layer (60 to 90 km), E-layer (90 to 150 km), F-layer (150 to 800 km), and a hypothetical G-layer. NO+ and O2+ ions dominate in the D and E layers, O+ in the F layer. Scientists are not in agreement about whether this layer model is valid, or where its boundaries should be set. See also Heaviside layer.

- The ionosphere strongly reflects RF waves up to the HF (3-30 MHz) range, enabling them to propagate beyond the horizon.

- iOS

- Apple’s operating system for mobile devices, meaning iPhone, iPad, and iPod. It’s based on Mac OS X, and has a touch interface. Its chief rival is Google’s Android.

- IoT

- Internet of Things. Buzzword for the worldwide archipelago of all Internet-connected but non-computing devices, most of which fall into the category of embedded devices. The typical IoT gadget has at least one sensor, a wireless (Bluetooth, Wi-Fi, ZigBee, et al) or wired network connection, and a microcontroller that monitors sensor input and handles communication.

- IoT devices are a growing security concern. Many are small, cheap units for which security is at best an afterthought. It’s relatively easy for automated Internet attacks to find them, take them over, and make them part of a botnet.

- IP

- (1)

- Internet Protocol. The lowest-level protocol of the Internet, handling addressing and and routing, and therefore one of the two keystone protocols of the TCP/IP protocol suite. IPv4 (version 4) dates to 1981. It has 32-bit addresses, represented as four numbers from 0 to 255 separated by periods, e.g. 221.01.173.60.

- Originally, the class – A, B, or C – of an IP address defined which of its 32 bits were the network number, and which were the host number. Class A networks have an 8-bit network mask with the first bit always 0 (range 0.x.x.x to 127.x.x.x); Class B networks have a 16-bit network mask that starts with the bits 10 (128.0.x.x to 191.255.x.x); Class C networks have a 24-bit network mask that starts 110 (192.0.0.x to 223.255.255.x). Certain IP addresses in each class are reserved. Classes D and E don’t support routing.

- The approach since 1993 is classless inter-domain routing (CIDR), under which a network can subnet the host-number portion of its global IP address. A subnet mask specifies where an address’s boundary between network and host lies. Example: 221.01.173.0/24 denotes a 24-bit network address with 8 bits left for hosts on that network, so its subnet mask is 255.255.255.0. It can therefore have up to 254 hosts – not 256, because .0 and .255 have special meanings. The network could, say, internally treat the most significant bit of the 8-bit host address as the 25th bit of the network address, creating two distinct subnets with up to 126 (not 128!) hosts each. These subnets would be denoted as 221.01.173.0/25 and 221.01.173.128/25, with the “/25” indicating the revised subnet address length – 25 bits instead of 24.

- Setting the network number to all zeros means this network, while setting it to all ones means all networks. Likewise, setting the host number to all zeros or ones means this host or all hosts on this network. (Those are the special meanings cited above.) See DNS, NAT, URL.

- IPv6 (version 6), previously called IPng (next generation), came out in 1998, offering packet encryption, greater ease of configuration, less unwieldy routing tables, and vastly more addresses (2128 instead of 232). Whereas an IPv4 address is typically represented as four 8-bit decimal numbers separated by periods, the standard for an IPv6 address is eight 16-bit hexadecimal numbers separated by colons, e.g., 01AC:2055:11E9:0066:BF02:8733:470C:58A0. It doesn’t matter whether the letters are upper- or lower-case. IPv6 has still not been widely adopted as of 2013.

- Modern network gateways commonly use DHCP, meaning they assign a computer a new IP address each time it connects. On a Windows PC, the console command

ipconfig /alldisplays information about the computer’s current IP address – or addresses, if it has multiple connections. - (2)

- Industry Pack. A standard type of parallel-mounting daughtercard (a.k.a. mezzanine card) for a larger board. The standard was prepared by VSO (VITA Standards Organization) and SBS GreenSpring Modular I/O. IP modules exist in single size (1.8 × 3.9 inches) and double size (3.9 × 3.9 inches).

- (3)

- Intellectual Property. Commercially valuable information or rights – patents, copyrights, trademarks, software, processes, etc. Derided as “imaginary property” by open-source and free-software adherents. The term is sometimes used for code modules or pre-built libraries that can be purchased and dropped into a larger software project.

- IPA

- Isopropyl Alcohol. Another name for a form of propanol.

- IPC

- (1)

- Inter-Process Communication. Any method of sharing data between running processes on a system, including pipes (meaning the old Unix | operator), Unix domain sockets, shared memory, and message queues.

- (2)

- Inter-Processor Communication. A generic term for exchanging data between different processors in a multi-processor system. More specifically, it's also the name of a software package that manages this task for Texas Instruments OMAP modules.

- (3)

- Institute for Printed Circuits, originally. The organization later changed its name to the Institute for Interconnecting and Packaging Electronic Circuits (IIPEC), and then, in 1999, to just IPC. It’s the American standards body for design and manufacture of PCBs.

- (4)

- Instructions Per Clock. A measure of a microprocessor’s computing power: how many instructions it can carry out with each tick of its digital clock.

- IPFS

- Inter-Planetary File System. A hyperlinking protocol and file system for peer-to-peer networks. It uses content addressing rather than location-based server addressing.

- IPM

- Interior Permanent Magnet. A type of motor in which permanent magnets are embedded in the rotor, providing finer control and better efficiency than SPM (surface permanent magnet) designs.

- IPng

- Internet Protocol next generation. Another term for IPv6. See IP.

- IPoS

- Internet Packet over Satellite. Standard approved by TIA and ETSI for two-way Internet access via satellite. It uses the Ku band (susceptible to rain fade – see microwave band) and a transmit power of 1, 2, or 4 watts.

- IPS

- Intrusion Prevention System. A combination of policies, procedures, and software/hardware tools for defending a network against malware. Also called IDPS (Intrusion Detection and Prevention System).

- IPsec

- Internet Protocol Security. A member of the TCP/IP protocol suite at the Internet layer, IPsec is a protocol suite itself. It encrypts connections at the IP packet level rather than at the Application layer, which is meant to provide uniform security for all network applications, and more trustworthy authentication.

- IPv6

- Internet Protocol version 6. See IP.

- IPX/SPX

- Internet Protocol Exchange (or Internetwork Packet Exchange)/Sequenced Packet Exchange. A Novell network protocol suite used by Novell NetWare, but marginalized by the ubiquitous TCP/IP. The address is a 4-byte network number and a 6-byte node ID. The network node address is the MAC number.

- I/Q

- In-phase and Quadrature. The independent, orthogonal components of a complex sinusoid. In RF modulation, I and Q are the baseband channels or rails of a signal (typically but not always digital). The transmitter modulates the I rail data with a cosine wave, and the Q rail with a sine wave. This ensures that their instantaneous phase angles are 90° apart, so they can’t interfere with one another. The transmitter mixes them to generate the baseband waveform, and beats this signal with the RF.

- The receiver reverses the process, down-converting the signal to baseband and splitting it into an I and a Q rail, which it mixes with a cosine and a sine wave, respectively, to recover the data. Regardless of how many symbols (states) the RF signal has, the orthogonality of I and Q means that only two rails are required for modulation or demodulation. Just as it takes two eyes to accurately judge an object’s position and movement, two rails are necessary to distinguish signal phase from signal amplitude. For BPSK, however, Q is zero. See constellation, phasor.

- IR

- (1)

- Infra-Red. The infra-red part of the electromagnetic (EM) spectrum begins where the low-frequency part of the visible light range ends. Since the performance of the human eye is variable, the boundary is only approximately a wavelength of 770 nm, and humans do have some limited ability to see into what’s considered the near infra-red.

- Different professions, professional organizations, and even companies have settled on their own naming conventions for portions of the infra-red spectrum. These conventions conflict and overlap, so the wavelength ranges in the table below are approximate at best. The exact numbers depend on who’s talking.

- Thermal or blackbody IR, radiated by all objects warmer than absolute zero – in other words, per the Third Law of Thermodynamics, all objects – has wavelengths from approximately 3000 to 100,000 nm. Infra-red cameras generate false-color images showing this radiation. Brighter objects in such images are not necessarily hotter; the amount of IR radiation an object emits does increase with temperature, but also varies with its material composition, in accordance with a property called emissivity.

- (2)

- Ionizing Radiation. What most people mean when they say “radiation”: EM waves and subatomic particle emissions capable of damaging matter at the atomic level. This includes all EM frequencies above near ultraviolet (see light). Frequencies below that range are called non-ionizing radiation (NIR). Fast-moving, charged subatomic particles (protons, electrons, positrons, etc. – see alpha particle, beta particle) are classed as directly ionizing particle radiation. Energetic uncharged particles (e.g. neutron radiation) can be indirectly ionizing by causing the release of charged particles or ionizing rays.

- IRC

- Internet Relay Chat. A member of the TCP/IP protocol suite at the Application layer. The IRC protocol allows multiple users to transmit text to a scrolling display, making it the forerunner of IM and texting.

- IrDA

- Infra-red Data Association. A trade association for creating infra-red standards commonly used to link peripherals to computers, such as IrDA Data (line-of-sight, ~1m range) and IrDA Control (multi-device, ~5m range).

- Iridium

- Worldwide mobile phone service (a consortium of 17 companies, led by Motorola), launched in 1998, bankrupt in 1999, and bought for a song by a new consortium. Named for the element iridium, atomic number 77, which is the number of satellites originally planned. It has 66 birds and 6 spares in six 780-km altitude, 100-minute period LEO orbits inclined 86.4° to the equator, all operated by Boeing. Signals are at 1616.0-1626.5 MHz from space to ground and in the Ka band (~30 GHz) from satellite to satellite. Its signals use a combination of FDMA and TDMA, and provide 2400 b/s data (more with compression).

- The Motorola handsets are relatively large and don’t work indoors, so the system can’t compete with traditional cellular service. Failure to recognize this was one of the original consortium’s biggest mistakes. Due to the inter-satellite links, quality and reliability of connections is less than those of rival systems. Its selling point is genuinely global coverage (apart from a few countries blacklisted by the US), so its principal customers are government. Compare Globalstar, ICO, Inmarsat, Orbcomm.

- IRQ

- Interrupt Request. A hardware event that interrupts what a processor is doing to activate some function or service. In early PCs, each IRQ was typically mapped to a single, specific device. The PC-AT had 15 IRQs, only about half of which could be assigned by the user.

- IS-136

- Interim Standard 136. Also called D-AMPS, EIA/TIA-136, and the US Digital Standard (USDS). Combined with IS-54, it was an unsuccessful rival to IS-95 as a specification for a 2nd generation (2G) U.S. digital cellular system using DQPSK modulation and TDMA with FDM. It uses the same spectrum as AMPS: 832 channels with 30 kHz channel spacing, receiving channels at 869-894 MHz, and transmitting channels at 824-849 MHz. Maximum channel rate is 48.6 kb/s. Replacing it with a 3G system would require more bandwidth than the 30 kHz channels. EDGE Compact, a standard defined for the U.S. market, would have allowed EDGE to fit into IS-136 without changing network frequencies.

- IS-2000

- Interim Standard 2000. An obsolete 3rd generation (3G) U.S. cellular system. It was designed to overlay existing IS-95 networks without new frequency allocations.

- IS-54

- Interim Standard 54. From ANSI. See IS-136.

- IS-95

- Interim Standard 95. Also called cdmaOne and EIA/TIA-95. An obsolete 2nd generation (2G) U.S. digital cellular system that used QPSK/OQPSK modulation and narrowband CDMA with FDM. It offered 20 channels (798 users/channel) with 1250 kHz channel spacing. Its receiving channels were at 869-894 MHz, and transmitting channels at 824-849 MHz. Maximum channel rate was 1.2288 Mb/s. See IS-2000.

- ISA

- (1)

- Industry Standard Architecture. The standardized version of the 8-bit, 5V or 12V, 4.77 MHz system bus used in the IBM PC and PC-XT (1981-1983), expanded to support 16-bit, 8.33 MHz boards for the PC-AT (1984), used in almost all PC clones, and now obsolete. See EISA.

- The ISA controller for an expansion device is on the plug-in board, not on the motherboard. Boards are typically 12.4" × 4.8", and have 31 (8-bit) or 49 (16-bit) pairs of contacts on the mating edge. Besides its obvious role as an expansion bus, ISA also supports low-speed functions such as the keyboard, serial ports, and floppy drives. See PC/104.

- (2)

- Instruction Set Architecture. The blueprint for building a CPU, implementing a specific hardware instruction set. Common ISA families include x86, ARM, and PowerPC.

- ISDB

- Integrated Services Digital Broadcasting. Japanese digital TV (DTV) standard also adopted by Brazil that relies on MPEG-2 video & audio compression, and MPEG-2 or -4 transport. There’s ISDB-S (satellite), using PSK in the 12 GHz band; ISDB-T (terrestrial RF), using COFDM with PSK/QAM in the VHF/UHF band; ISDB-C (cable); and a 2.6 GHz mobile type. Compare ATSC, DVB.

- ISDN

- Integrated Services Digital Network. A digital subscriber line technology overtaken by DSL and cable modems. An ISDN connection’s basic-rate interface (BRI) runs full duplex on a twisted pair at 80 kBaud (160 kb/s, QPSK): 144 kb/s via one delta (D) and two bearer (B) channels, 12 kb/s for framing, and 4 kb/s for a maintenance channel. The two bearer channels are 64 kb/s each – standard digital phone lines – but can be combined to support a single 128 kb/s connection. The 16 kb/s delta channel is for signaling: call setup, call progress, packet data where applicable, etc. Primary-rate ISDN runs over four wires and is a full T1 (1.544 Mb/s) or L1 (2.048 Mb/s), depending on country, with either 23 or 30 bearer channels and one full 64 kb/s delta channel. Broadband ISDN (B-ISDN), based on ATM, runs at 155 Mb/s.

- ISI

- Inter-Symbol Interference. Transmitting symbol pulses in a band-limited channel causes them to spread slightly in time, so that each symbol interferes with the symbols preceding and following it. This is ISI. Boosting power won’t help, since that also boosts the interference.

- The solution is pulse-shaping so that, at the instant of sampling, the ISI from neighboring symbols is zero. Nyquist showed that sinc[x] function pulses, i.e. sin[x]/x, achieve this in a bandwidth that’s just half the symbol rate. This isn’t physically realizable. However, raised cosine (square-root raised cosine at each end) pulse shaping does nearly the same thing. It uses 110% to 135% of Nyquist bandwidth, depending on pulse rolloff.

- ISM

- Industrial, Scientific, & Medical. An unlicensed portion of the spectrum in North America and most of Europe, including the range 2400-2483.5 MHz. It’s used for Bluetooth, 802.11b, and 802.11g.

- iSIM

- integrated Subscriber Identity Module. See SIM.

- ISN

- Initial Sequence Number. A locally unique 32-bit value that TCP assigns to each connection it creates.

- ISO

- (1)

- International Organization for Standardization, in English. The initials are a compromise in that they don’t quite match the name in any member state’s language, plus isos is Greek for “equal”. ANSI is the US delegate. Founded 1946, responsible for the OSI model.

- (2)

- A format for an archived, compressed image of an optical disc (CD or DVD), named for (1), which approved it. Imaging software reads the data from the disc and packs it into a file, usually with a .iso filename extension. Some operating systems can access an ISO as if it were the original physical medium. Reversing the imaging process to create (burn) a new CD or DVD requires a utility that can unpack and parse the ISO – just copying the file to disc won’t work.

- GNU/Linux software installations are commonly available for download as ISO images.

- ISOC

- The Internet SOCiety. An international non-profit organization in Reston, VA that supports and hosts the IETF, IESG, and IAB. It’s governed by a board of trustees elected by its members.

- isolator

- See circulator.

- isoplanatic angle

- In adaptive optics (AO), the viewing angle θ0 over which phase distortion has a variance less than 1 radian square. Think of it as the angular distance from the viewing axis at which AO correction starts making an optical image worse.

- isotropic

- Isotropic radiation is emitted uniformly in a sphere with transmitter power Pt and unity gain, yielding power density P = Pt/4πR² at distance R. This is a theoretical antenna model, since all real antennas have at least some directionality – transmit antenna gain Gt will be less than unity (1) in some directions and more in others. Isotropic is not the same as omnidirectional. See dBi.

- ISP

- (1)

- Internet Service Provider. Most of the early ISPs were former BBS operators changing with the times.

- (2)

- In-System Programmability. The capability of a programmable device – microprocessor, microcontroller, EEPROM, PLD, etc. – to be re-programmed without being removed from the system of which it’s a part.

- ISR

- (1)

- Interrupt Service Routine. A software function, usually very short, that’s called by a processor in response to an interrupt request (IRQ).

- (2)

- Intelligence, Surveillance, Reconnaissance. See C3I, C4I.

- Itanium

- See Intel.

- ITER

- International Thermonuclear Experimental Reactor, originally, but after negative public reaction to the coupling of the words “thermonuclear” and “experimental”, the organization linked its name to the Latin iter (road, direction, way). Project to develop a viable tokamak fusion reactor at Cadarache in southern France. Way behind schedule and over budget as of 2022. It’s mainly a EU show, but many other countries are participating.

- iterative code

- See FEC.

- ITO

- Indium Tin Oxide. See semiconductor.

- itrace

- ICMP Traceback. Proposed (2001) but never adopted ICMP change that would enable tracing IP traffic to its source by requiring the injection of trace packets.

- ITS

- Incompatible Timesharing System. A now-obsolete OS written (in assembly language) at MIT in the late 1960s to run on the DEC PDP-10 mainframe. The name, a reaction to MIT’s Compatible Time-Sharing System (CTSS), is pure hacker attitude.

- ITU

- International Telecommunications Union. Founded in 1946 and based in Geneva, this organization, now an agency of the UN, has absorbed the old CCITT and CCIR. It’s divided into three sectors: ITU-R (radio), ITU-T (telecom standardization), and ITU-D (development). ANSI is the American representative to ITU-T.

- ITX

- ?Information? Technology Extended. A set of PC motherboard/chassis specifications from VIA Technologies. Mini-ITX (2009) has a 170 × 170 mm board that fits any ATX or micro-ATX chassis. Pico-ITX (2007) is 100 × 72 mm. Mobile-ITX is 60 × 60 mm. There are others.

- IVI

- Interchangeable Virtual Instrument. See VI.

- IVR

- Interactive Voice Response. “If you know your party’s extension, press 1. To reach the billing department, press 2…”.

- IXC

- Inter-Exchange Carrier. A company that provides long-distance telephone service, i.e. between LATAs. See divestiture.

- IXP

- Internet Exchange Point. A network switch installation through which private networks (particularly ISPs) in the same geographical area can exchange traffic without going through the Internet proper. Besides being faster, this can save the networks money, since the traffic isn’t being handled by their Internet transit providers.

| Wavelength (nm) | Names |

| 770 - 1300 | IR-A, near infra-red (NIR) |

| 1300 - 3000 | IR-B, short-wave infra-red (SWIR) |

| 3000 - 8000 | IR-C, mid-wave infra-red (MWIR), mid-infra-red (MIR), intermediate infra-red (IIR) |

| 8000 - 15000 | IR-C, long-wave infra-red (LWIR) |

| 6000 - 40000 | IR-C, far infra-red (FIR) |

| 40000 - 1000000 | IR-C, far-far infra-red |